# Embedded Software CS 145/145L

#### Caio Batista de Melo

CS145 - Spring '22

## Announcements (2022-04-07)

• Homework #1 is due tomorrow!

- You should have started the project 1 already!

- Due date for partner formation is tomorrow as well

- Cross Compilation

- GPIO => State(s) ON and OFF

1 and 0 +5V and GND

- SFRs have a type and store data like variables.

- SFR => More than variables

PORT \*, PIN \*, DDR \* \* = A / B / C / D

• Bit manipulation

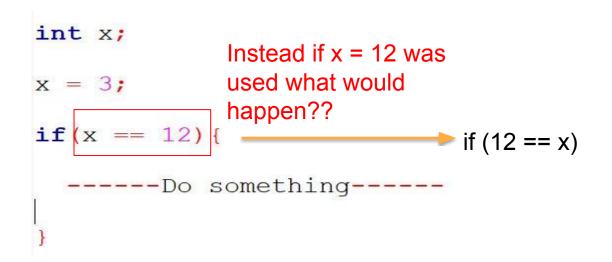

#### **Common Bug**

|                 | Operator | Description                        |  |  |  |  |

|-----------------|----------|------------------------------------|--|--|--|--|

| Not the as && a | and I    | bitwise AND<br>bitwise OR          |  |  |  |  |

| as ad           | <<       | bitwise exclusive OR<br>shift left |  |  |  |  |

|                 | >> ~     | shift right<br>one's complement    |  |  |  |  |

#### Setting bits to 1

If you need to turn on a specific bit, you can do this using the OR bitwise operation and a suitable mask. For example, if you need to turn on Bit 4 and Bit 7 of a byte (remember that the bit on the right hand side is Bit 0), you can use the mask 1001 0000 and the OR bitwise operation.

| Bit positio | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|-------------|---|---|---|---|---|---|---|---|

| Data        | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Mask        | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 |

| OR Resul    | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 |

#### You need bit-wise <u>OR</u> ("|") operation to <u>SET</u> a bit

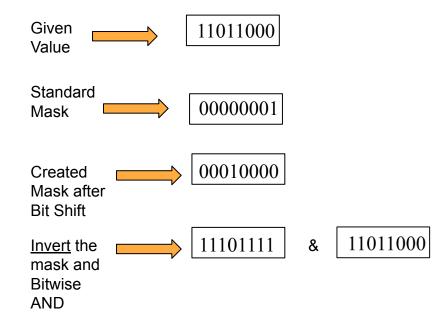

#### Resetting bits to 0

You can't force a bit to be 0 using the OR command. You can use the bitwise command AND along with a suitable mask, however. For example, suppose you wanted to reset Bits 0, 1 and 2 in a byte but leave all the other bits as they were. You would use the mask 1111 1000 along with the AND bitwise operator.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Bit position  |

|---|---|---|---|---|---|---|---|---------------|

| 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | Data          |

| 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | Mask          |

| 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | AND<br>Result |

#### You need bit-wise AND ("&") operation to CLEAR a bit

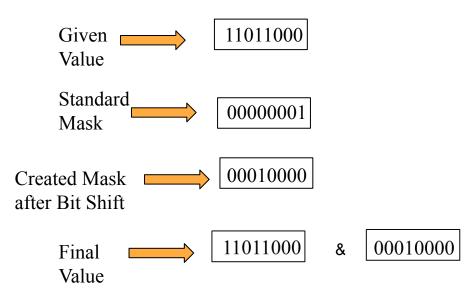

Consider you want to clear every bit except the bit in the 5<sup>th</sup> position

Solution:

- Create a standard mask (mask = 1)

- 2. Left shift it by four spaces (1 =>00010000)

- 3. AND it with the current value (value & 00010000)

Consider you want to clear the bit in the  $5^{\text{th}}$  position

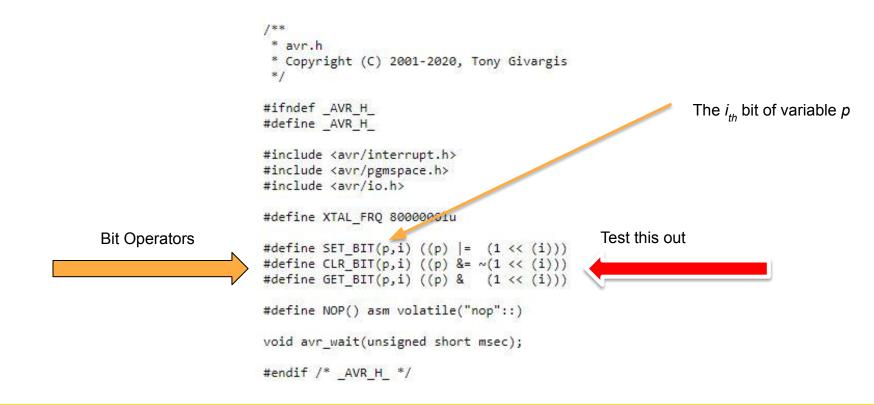

#### avr.h

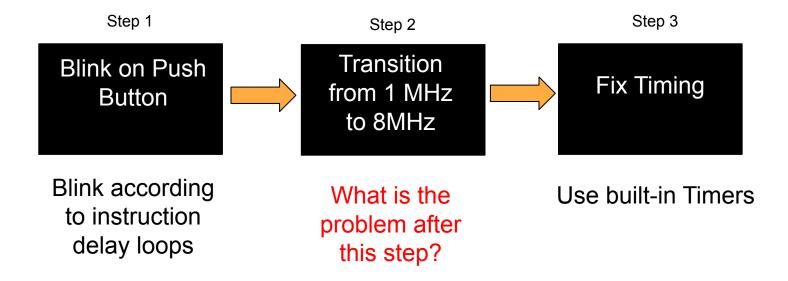

## 8 MHz Crystal

Image shown is a representation only. Exact specifications should be obtained from the product data sheet.

#### ATS08A

Digi-Key Part Number Manufacturer

Manufacturer Product Number

Supplier

Description

Manufacturer Standard Lead Time

Detailed Description

**Customer Reference**

Datasheet

CTX406-ND

**CTS-Frequency Controls**

ATS08A

**CTS-Frequency Controls**

CRYSTAL 8.0000MHZ 20PF TH

24 Weeks

8 MHz ±30ppm Crystal 20pF 60 Ohms HC-49/US

**Customer Reference**

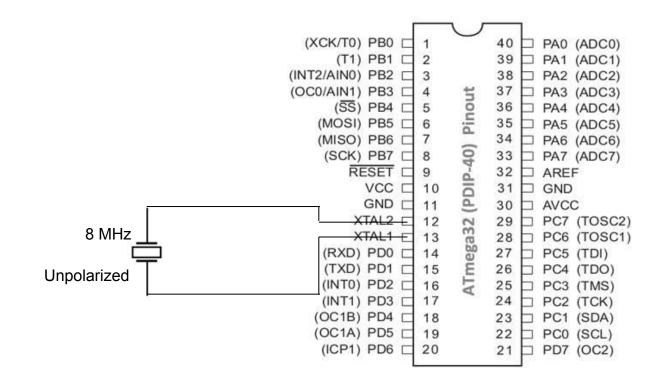

#### Adding 8 MHz Crystal (Hardware Method)

If you're using Microchip Studio:

- 1. You need to access the Fuse settings in Device Programming menu;

- 2. Last item in the list -> LOW.SUT\_CKSEL;

- 3. Last choice -> "Ext. Crystal/Resonator High Freq.; Start-up time: 16K CK + 64 ms";

- 4. DON'T CHANGE ANYTHING ELSE!

- 5. Click program and close!

Ref: <u>https://microchipdeveloper.com/8avr:avrfuses</u>

If you're using MPLAB X:

- 1. Window -> Target Memory Views -> Configuration Bits;

- 2. Click Read Configuration Bits;

- 3. Second item in the list -> FIELD == LOW.SUT\_CKSEL;

- 4. Choose "Ext. Crystal/Resonator High Freq.; Start-up time: 16K CK + 64 ms";

#### 5. DON'T CHANGE ANYTHING ELSE!

6. Click Program Configuration Bits and close this window.

#### Ref: <u>https://microchipdeveloper.com/mplabx:view-and-set-configuration-bits</u>

16

**GOOD LUCK :)**

#### .. .....

This might help though:

https://caiobatista.com/uploads/courses/uci/s22/cs145/avrdude-examples.pdf

If you're using something other than those (platformio?)...

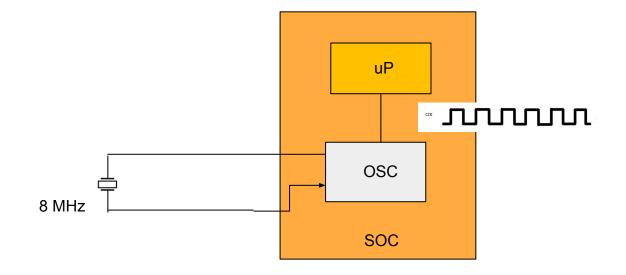

## Layout with Crystal

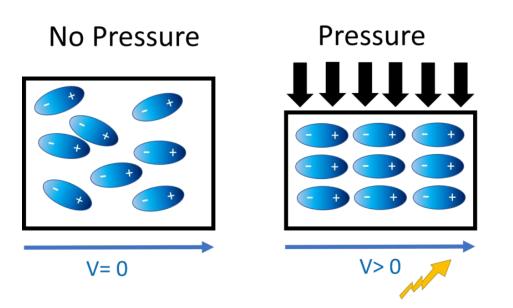

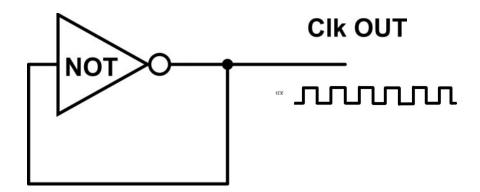

### Work of an Oscillator

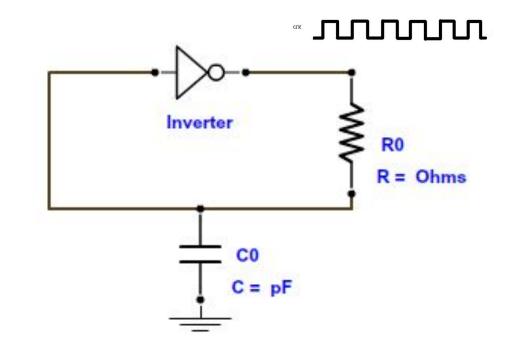

## Using R and C to control the Switching

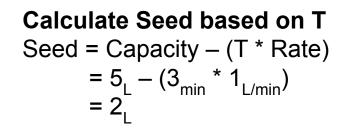

## **Timers - Bucket Analogy**

- Capacity

- Rate

- Overflow

- Seed

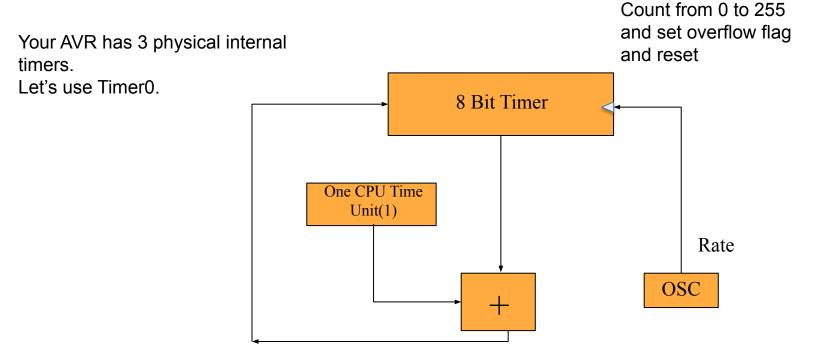

## **Timer Block Diagram**

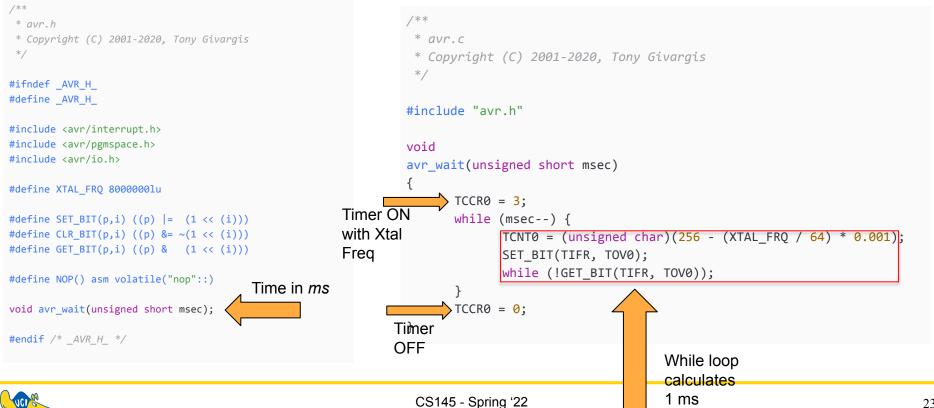

## Software to Work with a Timer

## **Turning the Timer On/Off**

TCCR0 = 3;

TCCR0 = 0;

.

.

## Timer/Counter Control Register – TCCR0 (Refer to page 80~82 on ATmega32 Manual)

#### • Bit 2:0 – CS02:0: Clock Select

The three Clock Select bits select the clock source to be used by the Timer/Counter.

Table 42.

Clock Select Bit Description

| CS02 | CS01 | CS00 | Description                                             |

|------|------|------|---------------------------------------------------------|

| 0    | 0    | 0    | No clock source (Timer/Counter stopped).                |

| 0    | 0    | 1    | clk <sub>I/O</sub> /(No prescaling)                     |

| 0    | 1    | 0    | clk <sub>I/O</sub> /8 (From prescaler)                  |

| 0    | 1    | 1    | clk <sub>I/O</sub> /64 (From prescaler)                 |

| 1    | 0    | 0    | clk <sub>I/O</sub> /256 (From prescaler)                |

| 1    | 0    | 1    | clk <sub>I/O</sub> /1024 (From prescaler)               |

| 1    | 1    | 0    | External clock source on T0 pin. Clock on falling edge. |

| 1    | 1    | 1    | External clock source on T0 pin. Clock on rising edge.  |

#### TCNT0 = (unsigned char)(256 - (XTAL\_FRQ / 64) \* 0.001);

# Timer/Counter Register – TCNT0 (Refer to page 82 on ATmega32 Manual)

| Bit           | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   | _ |

|---------------|------------|-----|-----|-----|-----|-----|-----|-----|---|

|               | TCNT0[7:0] |     |     |     |     |     |     |     |   |

| Read/Write    | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |   |

| Initial Value | 0          | 0   | 0   | 0   | 0   | 0   | 0   | 0   |   |

The Timer/Counter Register gives direct access, both for read and write operations, to the Timer/Counter unit 8-bit counter. Writing to the TCNT0 Register blocks (removes) the compare match on the following timer clock. Modifying the counter (TCNT0) while the counter is running, introduces a risk of missing a compare match between TCNT0 and the OCR0 Register.

## Waiting for Overflow

# SET\_BIT(TIFR, TOV0); while (!GET\_BIT(TIFR, TOV0));

# Timer/Counter Interrupt Flag Register– TIFR (Refer to page 83 on ATmega32 Manual)

Timer/Counter Interrupt Flag Register – TIFR

| Bit           | 7    | 6    | 5    | 4     | 3     | 2    | 1    | 0    | _    |

|---------------|------|------|------|-------|-------|------|------|------|------|

|               | OCF2 | TOV2 | ICF1 | OCF1A | OCF1B | TOV1 | OCF0 | TOV0 | TIFR |

| Read/Write    | R/W  | R/W  | R/W  | R/W   | R/W   | R/W  | R/W  | R/W  | -    |

| Initial Value | 0    | 0    | 0    | 0     | 0     | 0    | 0    | 0    |      |

#### • Bit 1 – OCF0: Output Compare Flag 0

The OCF0 bit is set (one) when a compare match occurs between the Timer/Counter0 and the data in OCR0 – Output Compare Register0. OCF0 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, OCF0 is cleared by writing a logic one to the flag. When the I-bit in SREG, OCIE0 (Timer/Counter0 Compare Match Interrupt Enable), and OCF0 are set (one), the Timer/Counter0 Compare Match Interrupt is executed.

#### • Bit 0 – TOV0: Timer/Counter0 Overflow Flag

The bit TOV0 is set (one) when an overflow occurs in Timer/Counter0. TOV0 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, TOV0 is cleared by writing a logic one to the flag. When the SREG I-bit, TOIE0 (Timer/Counter0 Overflow Interrupt Enable), and TOV0 are set (one), the Timer/Counter0 Overflow interrupt is executed. In phase correct PWM mode, this bit is set when Timer/Counter0 changes counting direction at \$00.

# See you next time :)

**Q & A**